沙特研究员开发全新3D堆叠晶体管,改善AR/VR等设备穿戴设备性能

查看引用/信息源请点击:techxplore

改进的性能和能效可以带来更高响应度和身临其境的用户体验

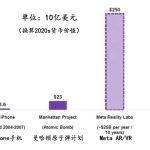

(映维网Nweon 2024年08月05日)晶体管是一系列电子器件的核心,起着放大和开关电信号的作用。电子工业的一个关键目标是继续提高晶体管的性能和能效,同时缩小它们的尺寸。

日前,沙特阿卜杜拉国王科技大学的研究人员开出了一种可以垂直堆叠在一起的全新3D堆叠晶体管

。据悉,他们能够堆叠出迄今为止最多数量的晶体管,并显著了提高电子设备的性能。

团队指出,所述技术能够支持诸如AR/VR等可穿戴设备,改进的性能和能效可以带来更高响应度和身临其境的用户体验。

随着技术的发展,行业对更强大、更高效、更紧凑电子设备的需求正不断增长。然而,传统的平面晶体管正在达到其物理和性能极限,限制了它们满足需求的能力。

所以,团队一直在努力克服这一挑战,以及寻找可以进一步提高晶体管性能的新材料或设计。

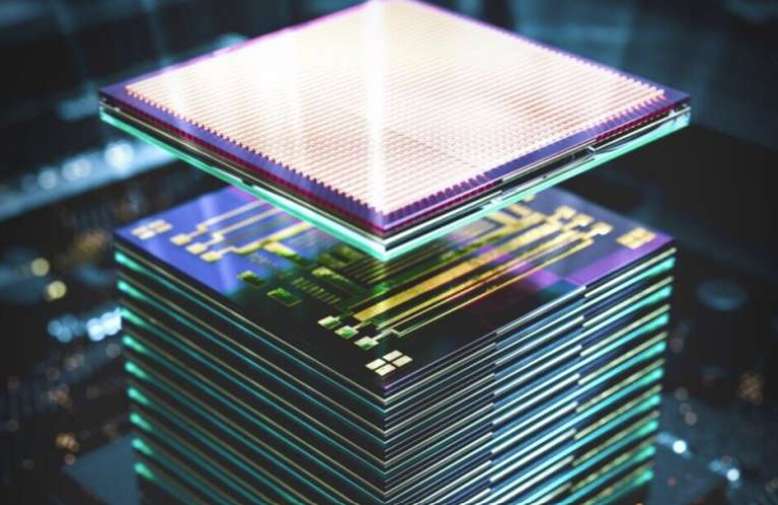

在日前公布的一份研究中,他们特别评估了垂直堆叠晶体管的可能性:将晶体管堆叠在一起,这样可以增加晶体管密度,从而提高电子产品的性能。

他们解释道:“我们研究的第一个目标是增加晶体管密度。通过开发低热预算和低界面粗糙度的技术,我们已经构建出10层纳米厚的化合物半导体晶体管。我们的目标是最大限度地利用晶圆空间。这种垂直堆叠方法允许更多的晶体管集成到给定的区域,从而显着提高处理能力和效率。”

研究人员介绍的设计可以在CMOS兼容的硅/二氧化硅衬底垂直堆叠十层氧化铟薄膜晶体管。这种垂直设计最大限度地利用晶圆空间,晶体管密度相较于平面设计更大。

他们指出:“晶体管安排在多层结构中,每一层都独立工作,但它们一起有助于整体性能。之选择氧化铟作为半导体材料,是因为它具有优异的电性能和与室温加工的兼容性。对于介电层,我们选择了parylene-C,它可以在室温下沉积并提供有效的绝缘。”

为了制造晶体管,研究人员首先在硅/二氧化硅晶片之上沉积了一层薄薄的In2O3。这种沉积层形成了电流流过的通道。

在In2O3层之后再沉积一层聚对parylene-C。这种材料充当电介质,令每个晶体管层绝缘,并防止层之间的电干扰。

晶体管的每一层都采用了先进的72步光刻工艺,而这个过程比典型的10步过程要复杂得多。他们解释道:“每一步都需要精确的对准和剂量优化,以确保每一层的完整性和性能。”

研究人员重复了多次沉积和图案步骤,直到堆叠出十层晶体管。其中,每一层都仔细地与其他层对齐,以确保设备的正确功能和之间的连接。

这个研究小组引入的新的垂直设计可以在给定区域内实现更大的晶体管密度。研究发现,这可以转化为更高的处理能力和效率。

他们指出:“In2O3和parylene-C层都是在室温下加工,这使得制造过程更加节能,并与现有的半导体制造技术兼容。我们的晶体管的电气特性,包括最大场效应迁移率为15 cm2/V-1s-1,亚阈值斜率为0.4 V/dec-1,电流开/关比高达108,超过了一系列现有的薄膜晶体管。这带来了更快的切换速度,更低的功耗,并提高了整体性能。”

团队表示,所述技术可以帮助用于增强广泛的消费电子产品,包括AR/VR系统:“改进的性能和能效可以带来更高响应度和身临其境的用户体验。”

......(全文 1237 字,剩余 119 字)

请微信扫码通过小程序阅读完整文章或者登入网站阅读完整文章

请微信扫码通过小程序阅读完整文章或者登入网站阅读完整文章

映维网会员可直接登入网站阅读

PICO员工可联系映维网免费获取权限